Set up in 1980, the second-level discipline Circuits & Systems of Tsinghua University was approved as a master program of Signals, Circuits and Systems in 1986, changed to Circuits and Systems Discipline in 1989, allowed to confer a doctorate degree in 1990 and rated as a national key discipline in the evaluation of previous disciplines of the Ministry of Education. By the end of 2011, more than 250 master students, more than 50 doctoral students and 8 postdoctoral fellows were trained in this discipline. It now has 18 doctoral students and more than 30 master students. It now has 2 professors, 6 associate professors, 2 lecturers, and 6 postdoctoral fellows. 9 of 10 teachers have a doctoral degree. This discipline has always focused on integrated circuits, and mainly carries out the work of the following four directions.

1. Electronic System Design Automation

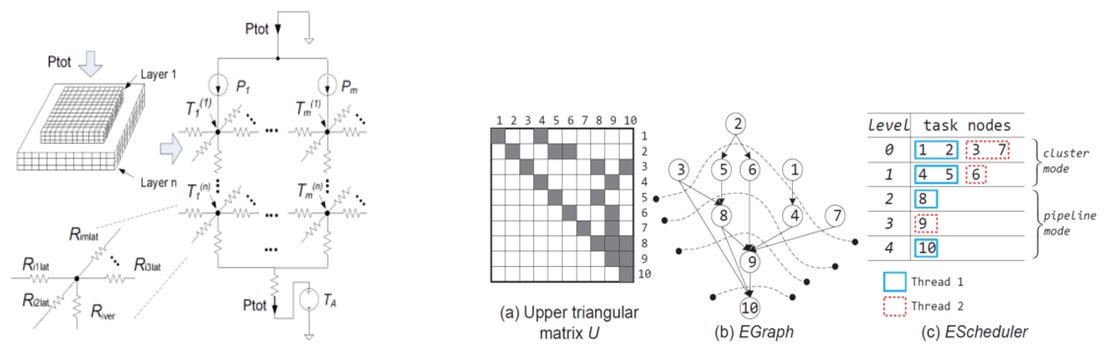

It has successively achieved pioneering achievements in computer-aided design, fast circuit simulation, and parallel circuit simulation of color TV sets. In recent years, around the characteristics of microsystem chips in the nano era, it has mainly studied multi-core structure and system design tools, 3D chip structure and design tools, parallel circuit simulation, power/thermal analysis and low-power design, radiation resistance/NBTI and high-reliability circuits, etc.

Piecewise linear leakage power model and coarse-grained thermal analysis method [DATE 2007] |

Parallel circuit simulation: NICS-LU [TCAS II, ASPDAC 2012 Best Paper Award Nomination, DAC 2012] |

2. Analog and Digital-analog Hybrid Integrated Circuits

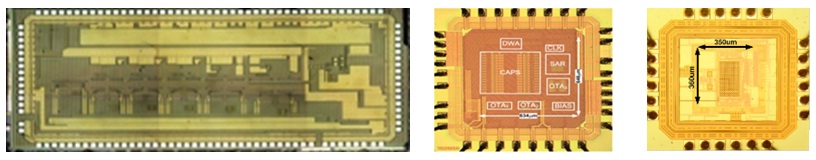

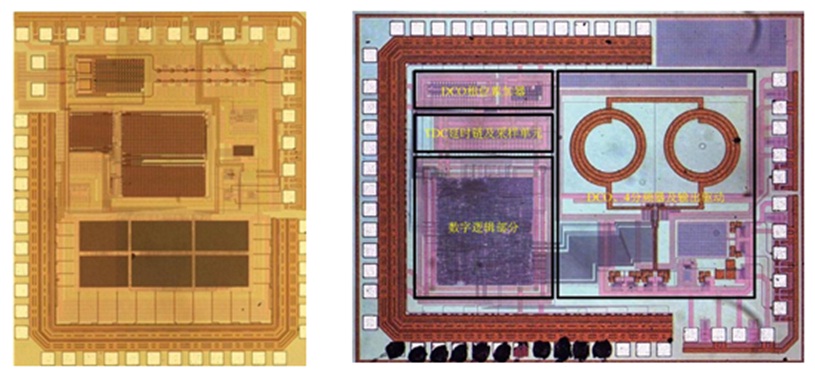

Mainly study high-speed, high-precision, low-power ADC and DAC. 12bit 200MS/s ADC, 12bit 100kS/s digital correction SAR ADC was successfully designed by use of 0.18um process. Spurious-free dynamic range (SFDR) reached 90.36dB and was the highest in the similar literature reported, reaching the international leading level; 12bit 100kS/s low-power consumption ADC has a power consumption of only 1.92uW; 24bit audio?? ADC has a power consumption of 20mW; the 14bit 1GS/s DAC and 20-bit audio were successfully designed by use of 0.13um process?? DAC; the 16bit audio was successfully designed by use of 65nm process?? ADC has a power consumption of only 371uW.

ADC and DAC micrographs (designed in 2007): 12bit 200MS/s ADC, 16bit audio SD ADC, 12bit 100kS/s ADC

3. Communication and Digital Media Processing

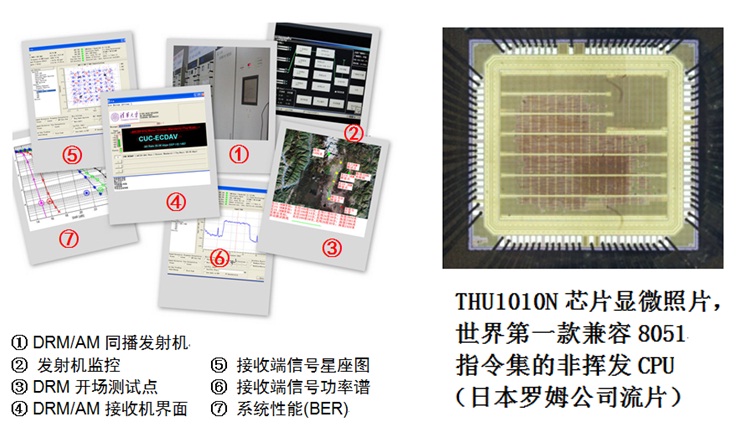

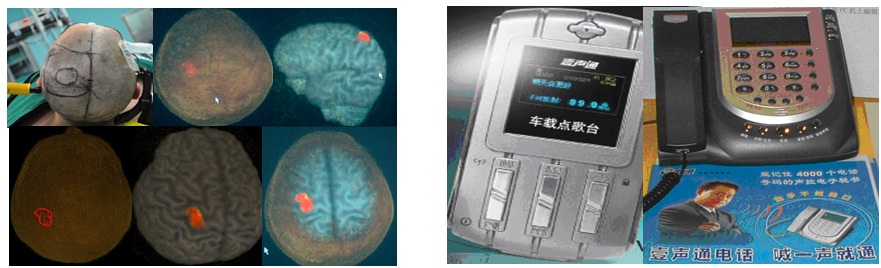

It began to study digital audio signal processing technology in 1992, and undertook a major industrialization project of the State Scientific and Technological Commission "Research on Key Technologies of Digital Audio Broadcasting Receivers". At the end of 1996, the first digital audio broadcasting receiver in China was trial-produced and the site receiving was successfully conducted on Foshan Digital Audio Broadcasting Pilot Network. The DRM broadcasting receiver completed in 2007 has FM sound quality, news, weather forecast, real-time dynamic traffic information distribution and intelligent navigation functions. It has cooperated with Communication University of China in successfully conducting many DRM opening tests in Lijiang, Changsha and other cities.

This discipline has also made many breakthroughs in audio coding and detection, which have been applied in the retrieval of sports highlights; the medical multi-modal data information fusion achievements are tried out in the brain tumor surgery assisted system.

The voice recognition algorithms and chips completed by the Circuits and Systems Discipline after more than ten years of unremitting efforts have been successfully applied to many commercial products.

This discipline has recently made breakthroughs in ultra-low power consumption non-volatile CPU, bridge structure detection, and research on protection of rare animals.

4. CMOS Radio Frequency Integrated Circuit

CMOS radio frequency circuit is the difficulty and bottleneck of designing broadband wireless mobile communication network system chips. Several phase-locked loops have been designed in this discipline and have been subject to tape-out verification. The low-power phase-locked loop designed in 2010 has an operating frequency of 1.72 GHz-1.74 GHz, a phase noise of -119.3 dBc/Hz@1 MHz, a settling time of 18 µs-25 µs, and a power consumption of only 10.6 mW. The all-digital phase-locked loop designed by this discipline in 2010 has a locking time of only 12µs.

Low power consumption ∑-△ Fractional-N PLL |

All-digital phase-locked loop |

Institute of Circuits & Systems

![]()